*算术逻辑单元(ALU)**:是运算器的核心,所有计算操作都在 ALU 中完成。···

1. CPU 的基本组成

CPU(中央处理器)是计算机的核心部件,主要由以下几个部分构成:

l 运算器:负责数据的算术和逻辑运算;

l 控制器:负责指令的取指、译码和执行控制;

l 寄存器组:包括通用寄存器和专用寄存器(如程序计数器 PC、指令寄存器 IR、状态寄存器等),用于暂存指令、数据和地址;

l 内部总线:连接 CPU 内部各部件,实现数据、地址和控制信号的传输。

这些部件通过内部总线相互连接,协同工作。例如,在图 1-1 的结构示意图中,可以看到运算器与控制器之间通过内部总线交换数据和控制信号,寄存器组为两者提供高速存储支持。

2. 运算器的核心说明

运算器是 CPU 中执行数据处理的核心功能单元,其主要组成部分包括:

l 算术逻辑单元(ALU)

l 累加寄存器(AC)

l 数据缓冲寄存器(DR)

l 状态条件寄存器(PSW)

它的核心功能包括:

l 执行基本的算术运算:如加法、减法、乘法、除法等;

l 执行逻辑运算:如与(AND)、或(OR)、非(NOT)、异或(XOR)等;

l 进行逻辑测试:如比较两个数的大小、判断是否为零等,结果会影响状态寄存器中的标志位。

3. 运算器各组件功能详解

l 算术逻辑单元(ALU):是运算器的核心,所有计算操作都在 ALU 中完成。它接收来自寄存器的数据,根据控制信号执行相应运算,并输出结果。

l 累加寄存器(AC):一种专用的通用寄存器,用来暂时存放参与运算的操作数和中间结果。例如,在执行“A - B”时,A 被先加载到 AC 中,然后 ALU 使用 AC 中的值与 B 进行减法运算,结果通常也存回 AC。因此,AC 是 ALU 工作所必需的工作区寄存器。

l 数据缓冲寄存器(DR):用于暂存从内存读出的数据或将要写入内存的数据,起到隔离和缓冲作用,确保运算器与内存之间的速度匹配。

l 状态条件寄存器(PSW,Program Status Word):保存 ALU 运算后的状态信息,如进位标志(C)、零标志(Z)、负数标志(N)、溢出标志(V)等,这些标志会影响后续的条件跳转指令执行。

综上所述,CPU 通过运算器对数据进行加工,控制器协调整个流程,寄存器提供快速访问存储,内部总线保障通信,共同完成指令的执行。

控制器是 CPU 的核心组成部分之一,主要负责指挥和协调计算机各部件协同工作,确保指令能够正确、有序地执行。其核心功能是取指令、分析指令、执行指令,并产生相应的控制信号来驱动其他部件。

一、控制器的主要功能:

1. 取指(Fetch)

根据程序计数器(PC)中存储的地址,从内存中取出下一条要执行的指令,送入指令寄存器(IR)。

2. 译码(Decode)

对指令寄存器中的指令进行分析,确定该指令的操作类型(如加法、跳转等)和操作数地址。

3. 执行(Execute)

向运算器、存储器、I/O 设备等发出控制信号,完成指令所要求的操作。

4. 时序控制

提供定时信号(时钟脉冲),确保各个操作按规定的节拍有序进行。

5. 异常与中断处理

响应硬件中断或软件异常,暂停当前程序,转入相应的处理程序。

6. 更新 PC

在取指后自动递增 PC,指向下一条指令地址;若遇到跳转指令,则将目标地址装入 PC。

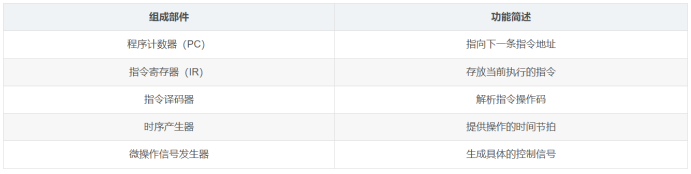

二、控制器的组成部件:

1. 程序计数器(PC, Program Counter)

又称指令指针(IP),用于存放即将执行的下一条指令在内存中的地址。

每次取指后,PC 自动加 1(或加上指令长度);

遇到转移指令时,PC 被更新为目标地址。

2. 指令寄存器(IR, Instruction Register)

存放当前正在执行的指令,直到该指令执行完毕。

3. 指令译码器(ID, Instruction Decoder)

对 IR 中的指令操作码进行译码,识别出具体操作(如 ADD、JMP 等),并生成对应的控制信号。

4. 时序产生器(Timing Generator)

产生时钟信号和操作周期信号(如取指周期、执行周期),为控制器提供时间基准。

5. 微操作信号发生器(Micro-operation Signal Generator)

根据译码结果和时序信号,生成一系列微命令(控制信号),如“打开总线门”、“启动 ALU”、“写寄存器”等,控制数据通路的动作。

6. 控制方式选择逻辑(可选)

区分微程序控制或硬布线控制两种实现方式:

l 硬布线控制器:用组合逻辑电路直接生成控制信号,速度快但设计复杂;

l 微程序控制器:将控制信号编成“微指令”,存于控制存储器中,灵活性高。

总结:

控制器通过上述部件协同工作,实现了对整个计算机系统的自动化控制。

扫一扫,关注我们